# Ka band power pHEMT technology for space power flip-chip assembly

E. ROGEAUX<sup>(1)</sup>, J-P. FRAYSSE<sup>(1)</sup>, C. SCHAFFAUSER<sup>(1)</sup>, S. GEORGE<sup>(1)</sup>,

D. PONS<sup>(2)</sup>, P. FELLON<sup>(2)</sup>, D. GEIGER<sup>(2)</sup>, D. THERON<sup>(3)</sup>, N. HAESE<sup>(3)</sup>, S. VERDEYME<sup>(4)</sup>,

R. QUERE<sup>(4)</sup>, D. BAILLARGEAT<sup>(4)</sup>, E. NGOYA<sup>(4)</sup>, S. LONG<sup>(5)</sup>, L. ESCOTTE<sup>(5)</sup>

<sup>(1)</sup>Alcatel Space Industries, 26 Av JF.Champollion, 31037 Toulouse Cedex, France

<sup>(2)</sup>United Monolithic Semiconductors, 91401 Orsay Cedex France

<sup>(3)</sup>Institut d'Electronique et Microélectronique du Nord, 59652 Villeneuve d'Ascq Cedex, France

<sup>(4)</sup>Institut de Recherche en Communications Optiques et Micro-ondes, 87060 Limoges Cedex, France

<sup>(5)</sup>Laboratoire d'Analyse et d'Architecture des Systèmes, 31077 TOULOUSE Cedex, France

**Abstract** — This paper proposes a released power pHEMT process for flip-chip mounting. The potential of this flip-chip process is demonstrated for power and low-noise applications in Ka-band.

## I. INTRODUCTION

Flip-chip technology (FC) is a promising candidate for the use in a new generation of broadband multimedia satellites where thermal management and miniaturisation are key enabling criterias. Applying flip-chip technology to high power GaAs devices (HBTs and pHEMTs) have been demonstrated by several Research Institutes and company's over the last few years with impressive results [1-5].

In this paper, we presented the work done inside the "Optimal" project (RNRT project) to adapt the power pHEMT process PPH25 from United Monolithic Semiconductors for the use of flip-chip assembly. Both the power performance and the low-noise performance of this process will be evaluated. This allows the fabrication of high-power and low-noise MMICs in one wafer run. An optimized layout of the flip-chip transistor cell shows a reduction of the thermal resistance compared to the standard configuration. A 3-D electromagnetic analysis, a non-linear electro-thermal model and a noise model will be presented. Thus all elements for the design of low-noise and high-power MMICs will be available.

## II. TECHNOLOGY DEVELOPMENT

The work is based on the PPH25 process (0.25 $\mu$ m power-pHEMT) of United Monolithic Semiconductors. In order to reduce the channel temperature of the transistors,

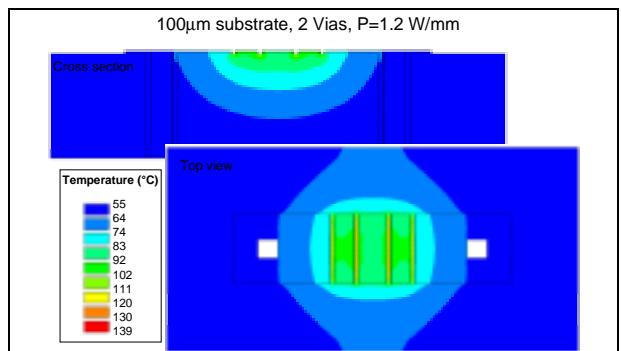

3-D simulations have been performed using the finite element method. As border conditions we took a temperature of 55 °C for the heat sink and a worst case approximation for the power dissipation of 1.2W/mm. A conventional structure (up-side up mounting, 100  $\mu$ m substrate thickness with via-holes) was calculated for the assessment and comparison of the different bump-configurations Fig.1.

Fig.1 : Thermal calculation of the conventional structure with 100  $\mu$ m substrate thickness an up-side up mounting.

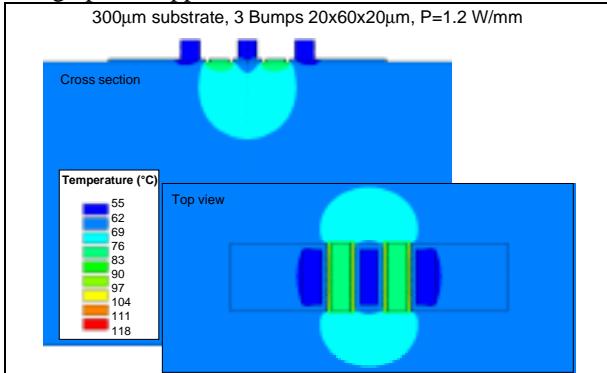

With the conventional configuration a maximum channel temperature of 139 °C is obtained. This result was compared to different flip-chip configurations. From this calculations we found that it is absolutely necessary to implement a thermal bump on each source pad. The results of the thermal calculations using a optimized bump configuration is shown in Fig.2.

With the optimized configuration we found a maximum channel temperature of 118 °C, which is indeed 21 °C lower as compared with conventional mounting.

This demonstrates the potential of the flip-chip mounting for high power applications.

Fig.2 : Thermal calculation of a flip-chip configuration with thermal bumps on each source pad.

The next step was the development of an appropriate bump technology. To avoid coupling between the CPW chip and the substrate a bump height of 30  $\mu\text{m}$  has to be realized. However the lateral size of the thermal bumps is limited as an increase of the transistor size leads to a degradation of the RF-performance. Taking this into account a lateral size of 20  $\mu\text{m}$  for the thermal bumps seems to be a good compromise between the RF-performance on the one hand and the technological difficulties as well as the thermal resistance on the other hand. A difficulty was to realize air-bridges and bump on the same transistor to have the possibility for on-wafer testing.

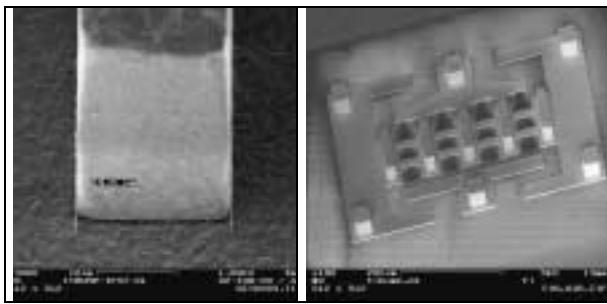

By implementing a probimid resist system and controlling the electroplating conditions, we succeed in the development of smooth bumps which are compliant with the above mentioned demands. The Au-bumps show a smooth surface and no porosity. Thus the bumps are well suited for the use of thermo compression mounting. The choice to use Au-bumps and consequently thermo compression mounting is due to the fact, that the Au-bumps show a superior thermal behavior compared to solder bumps Fig.3.

Fig.3 : Detail view of a rectangular bump and a multifinger transistor with thermal bumps on each source pad. :

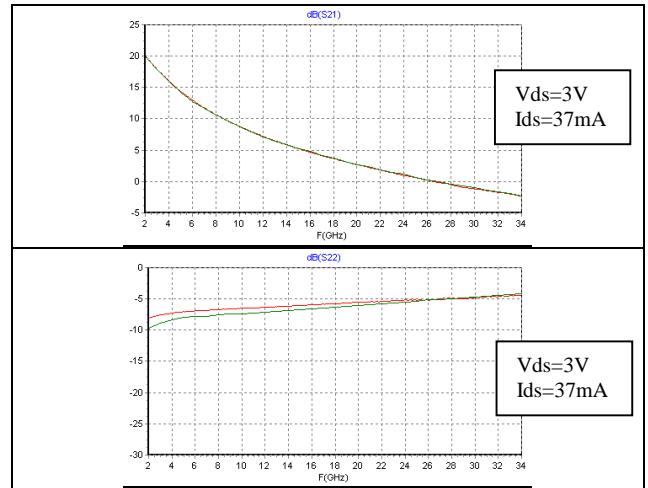

An electrical comparison of PPH25 standard transistors and transistors with thermal bumps on each source pad has been performed to evaluate the impact of increased source pad size. As shown in Fig.4, the effects are negligible up to 34 GHz.

Fig.4 : Transistors with and without bumps

### III. FLIP-CHIP MOUNTING EFFECTS

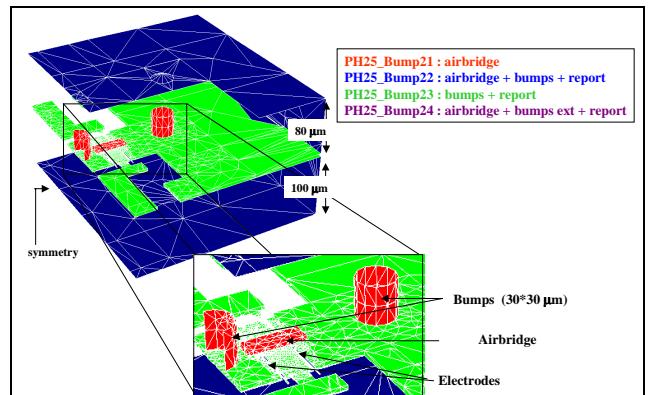

The coplanar technology is well suited for flip-chip mounting. So the second topic studied in the project was to define the impacts of parasitic effects of the flip-chip transitions. First the effects of a substrate over coplanar lines was investigated. Then the transistors with thermal bumps have been specially addressed (Fig.5).

Fig.5 : 3-D bumped transistors.

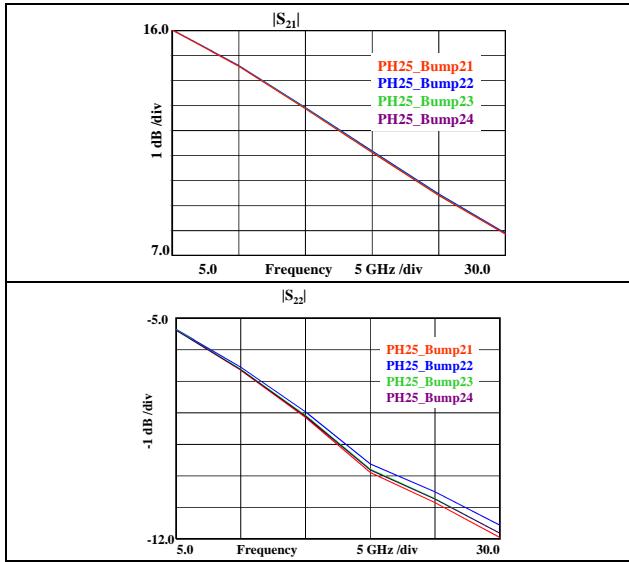

3-D simulations were performed applying an hybrid approach combining a Finite Element software developed at the IRCOM and a circuit one [6]. The results showed very little impact of carrier substrate on the transistor behavior up to 30 GHz as showed on Fig.6.

Fig.6 : 3-D-electromagnetic simulations of the flip-chip mounted transistors.

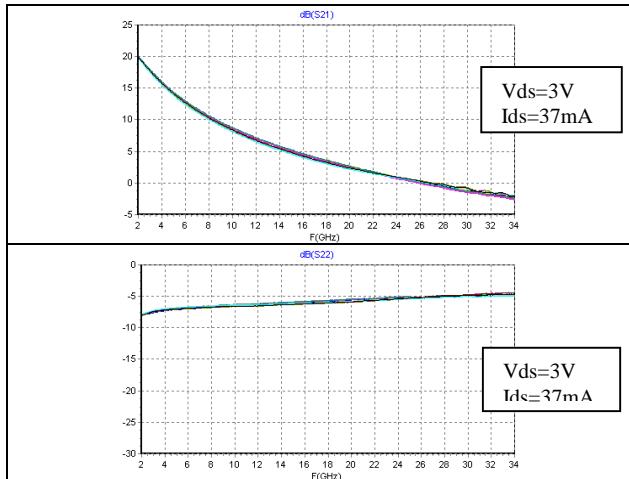

These simulated results have been validated by experiments: chips have been mounted on 635 $\mu$ m thick Alumina carriers and S-parameter measurements up to 34GHz have been carried out before and after the flip-chip mounting (Fig.7). The transistors showed a nearly identical behavior before and after the flip-chip mounting.

Fig.7 : S-parameters before and after flip-chip mounting

#### IV. ELECTRO-THERMAL NON LINEAR AND NOISE MODELING

##### Electro-thermal non linear modeling

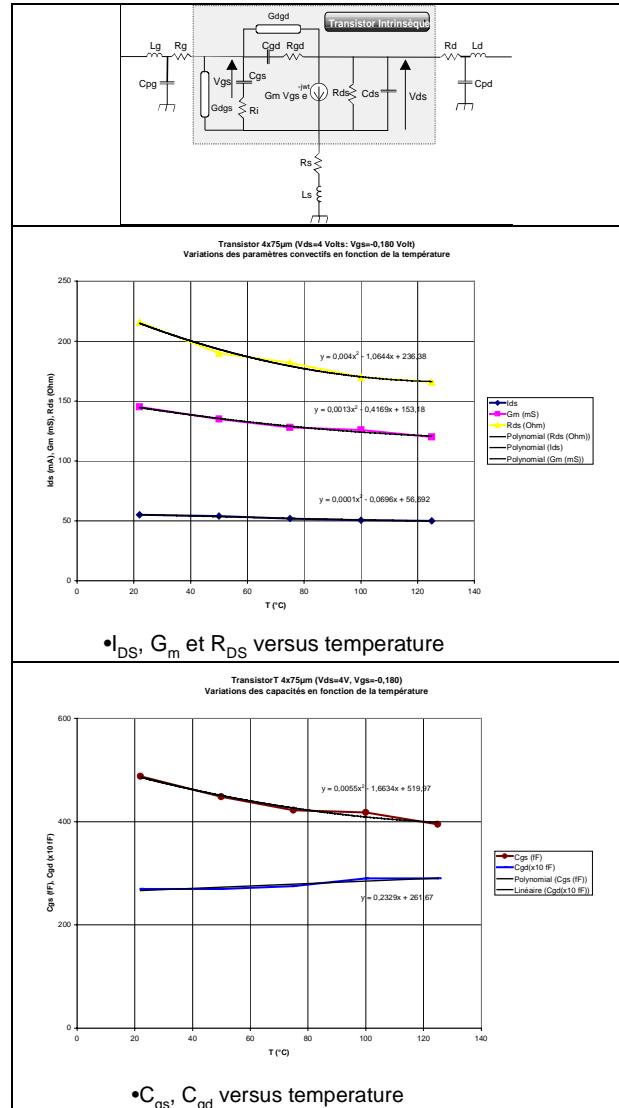

An electro-thermal model has been performed taking into account the bumps and thermal resistance of the transistors (Fig.8).

Fig.8 : Electro-thermal modeling of a 4x75 $\mu$ m transistor

CW mode and multi-tone simulations have been performed on 4x75 $\mu$ m and 8x75 $\mu$ m transistors. The optimum load impedances have been determined for the HPA design in K band to assume a NPR (Noise to Power Ratio) greater than 16 dB (Fig.9).

|              | Zopt     | PAE  | POUT   | GAIN  |

|--------------|----------|------|--------|-------|

| 4x75 $\mu$ m | 35+j36Ωm | ≤44% | ≤19dBm | ≥11dB |

| 8x75 $\mu$ m | 16+j18Ωm | ≤34% | ≤20dBm | ≥8 dB |

Fig.9 : Optimum load impedance (NPR>16dB)

##### Noise modeling

Despite the usage of a power process, the noise performance of the PPH25 process has been determined to allow the fabrication of LNAs and HPAs in one wafer run.

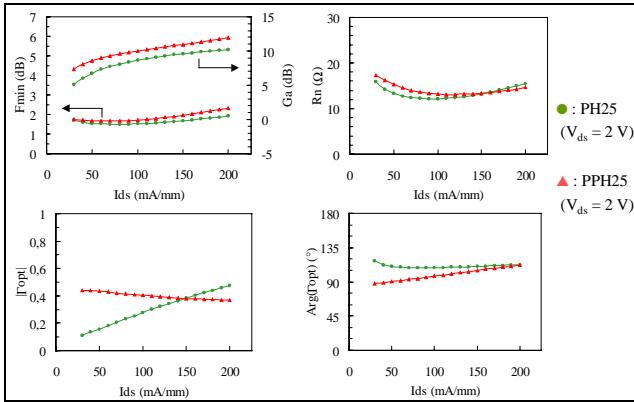

The use of the PPH25 process for low-noise applications at Ka-band is still reasonable as this process offers high gain and low capacities at this frequencies. In Fig.10 the results of the noise modeling of the PPH25 process are compared to the UMS low noise process PH25.

Fig.10 : PH25 and PPH25 noise parameters at 30GHz (4x30 $\mu$ m)

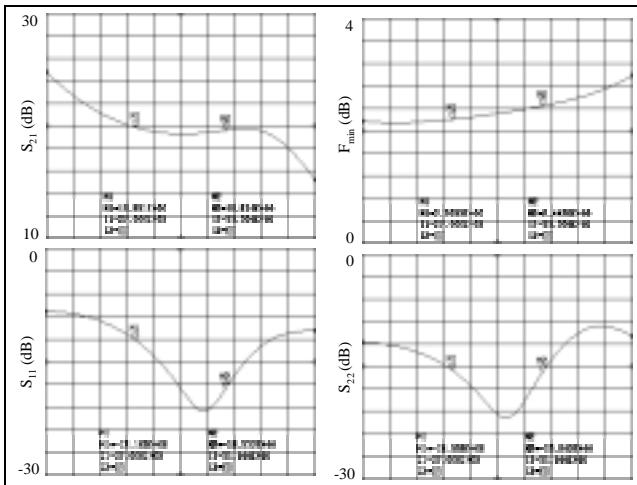

The PPH25 shows a very comparable noise behavior as the PH25 process. At 30 GHz a minimum noise figure below 2 dB and an associated gain in the range of 10 dB was found. This demonstrates that both, high power and low noise applications, could be addressed with the PPH25 process. A design of coplanar technology LNA at 30GHz based on 3 stages (6x30 $\mu$ m) biased at 13.5mA Vds=2V, is ongoing and previous simulation results based on CPW lines Heinrich models are given on Fig.11.

Fig.11 : LNA simulation results

## V. CONCLUSION

The power pHEMT process (PPH25) of United Monolithic Semiconductors has been extended for the use of flip-chip mounting. Thermal calculations showed that the maximum channel temperature could be decreased with the flip-chip approach. This was possible by adding thermal bumps on each source pad. From electromagnetic simulations and from S-parameter measurements up to 34 GHz, no negative effects of the flip-chip transitions were detected. A non linear electro-thermal model has been established for CW and multi-carrier simulations. From a noise modeling we found that this process could be used both for power applications and for low-noise applications at Ka-band.

The available technology (PPH25 for flip-chip) will be further validated by the realization of CPW high-power and low noise-amplifiers at Ka-band.

## ACKNOWLEDGEMENT

The authors would like to acknowledge the RNRT (Ministère de l'Education Nationale de la Recherche et de la Technologie, Direction de la technologie) for funding under the “OPTIMAL” contract (Optimisation en Puissance de Technologies Intégrées Millimétriques pour Amplification Linéaire). We also acknowledge Mr Jacques CITERNE from INSA/LCST, Rennes (France) for his expertise in the project.

## REFERENCES

- [1] D. Hill, T. S. Kim “28 V Low thermal Impedance HBT with 20 W CW Output power”, *IEEE Transactions on microwave theory and techniques*, pp. 2224-2228, vol. 45, N°12, Dec 97.

- [2] P. Cameron, W. Pan, C. Hanz, R. Nicklaus, P. Chu, D. Wong, T. Cisco “A flip-chip high efficiency X-Band HPA”, *1997 IEEE MTT-S Digest*, pp. 889-892.

- [3] O. Vendier, E. Rogeaux and al, “Power flip-chip assembly for space applications using HBT in Ku band” *22<sup>nd</sup> GaAs IC Symposium*, pp157-159, November 2000.

- [4] M. Schlechtweg and al ,”Coplanar MMICs up to 100GHz for communication and sensor systems”, *APMC’99*, Workshop1, November 1999.

- [5] A. Bessemoulin, M. Schlechtweg and al, “Design of coplanar power amplifiers for mm-wave system applications including thermal aspects”, *GAAS 2000*, pp224-227, October 2000.

- [6] E. Larique and al, “Linear and non linear FET modelling applying an electromagnetic and electrical hybrid software”, *IEEE Transactions on MTT*, vol 47, N°6, pp915-918, June 1999.